**35 GHz AND 60 GHz LOW NOISE HEMT MMIC AMPLIFIERS FOR CIVIL APPLICATIONS\***

P. BOURNE\*, P. ARSENE-HENRY\*, P. FELLON\*, D. PONS\*\*

\* THOMSON COMPOSANTS MICROONDES B.P. 46 - 91401 - ORSAY Cdx. FRANCE

\*\* LABORATOIRE CENTRAL DE RECHERCHE - 91404 - ORSAY Cdx. FRANCE

**ABSTRACT**

Monolithic HEMT low noise amplifiers have been developed for civil applications at Q and V bands. They consist of two stage amplifiers with  $0.25\mu\text{m}$  HEMTs. At 35 GHz and 60 GHz, they exhibit respectively more than 15 dB gain with 4 dB noise, and 12.5 dB gain with a noise figure between 5 and 6 dB over a 10 percent frequency range.

**INTRODUCTION**

As HEMT technology matures, the millimeter wave frequencies become more and more attractive for civil applications (car and other short distance communications,...). The challenge for the next few years is to propose reliable products at a low cost in these frequency ranges for civil applications.

HEMTs have already demonstrated their superiority when compared to MESFETs in millimeter frequencies, and results were reported on monolithic amplifiers [1] [2].

This paper describes the design, fabrication and measurements of low noise amplifiers working at 35 GHz and 60 GHz. Special efforts were made during the design to improve the stabilisation of the circuits at low

frequencies, employing simple, high yield elements. Measurements in test jigs were taken into account by modelling the associated bonding wires.

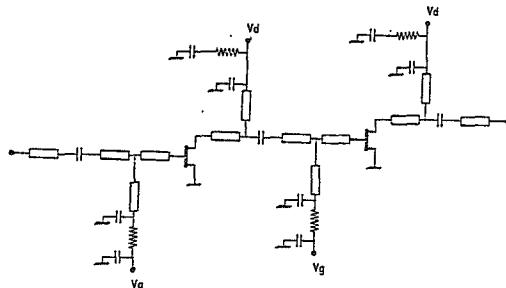

Fig 1 : Block diagramm of the 2-stage amplifiers

**CIRCUIT DESIGN**

Figure 1 shows the block diagram of the two stage amplifiers. The input, output and interstage circuits consist of low and high impedance series transmission lines. Losses of those lines were calculated by extrapolation from in house models which are validated up to 18 GHz. Discontinuity models derived from Gupta [3] are available in commercial simulators. Specific gate and drain networks were used for the stabilisation of the amplifiers at low frequencies. This stabilisation is essential for their future integration in a whole module. The damping is realised using RC circuits and the associated inductance of the bonding wires. The electric models of resistors and capacitances

IF1

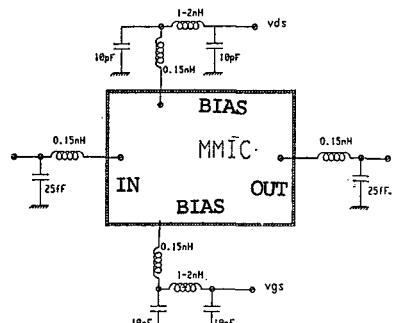

were extrapolated from these at 18 GHz. Connecting wires (input, output and bias) were taken into account in the simulation (fig.2) to anticipate the final results of characterization. To reduce this parasitic effect, open transmission line stubs were added in input and output network.

Fig 2 : Connecting wire model

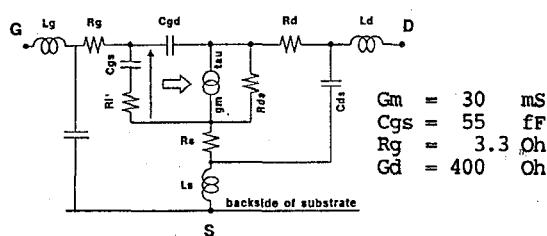

The active element of the two stage amplifiers is the GaAlAs/GaAs HEMT with a  $0.25 \mu\text{m}$  triangular gate. The equivalent circuit model is extracted from on-wafer S parameter measurements up to 40 GHz. Figure 3 shows the models for the maximum transconductance bias condition (at  $VG = 0\text{V}$ ). In fact, the two stages of the amplifiers were designed in this bias condition to get a high gain, and the input matching was optimized to get a minimum noise figure. Noise parameters are calculated from the circuit models and compared to measurements up to 40 GHz.

Fig 3 : 0.25um\*2\*25um HEMT circuit model

## CIRCUIT FABRICATION

The circuits were processed in the THOMSON COMPOSANTS MICROONDES foundry. They are composed of AlNi 0.25  $\mu\text{m}$  gate length HEMTs (fig.4),  $\text{Si}_3\text{N}_4$  overlay capacitors and via holes through a 100  $\mu\text{m}$  thick wafer. Figure 5 shows the HEMT epitaxial growth structure. The buffer layer is made of a 10 period (GaAs/AlGaAs) superlattice.

Fig 4 : 0.25um triangular gate detail

|                    |                                                                                                        |

|--------------------|--------------------------------------------------------------------------------------------------------|

| GaAs:Si            | $n = 4.0 \pm 0.3 \text{ cm}^{-3}$<br>$e = 500 \pm 15 \text{ \AA}$                                      |

| AlGaAs:Si          | $n = 2.0 \pm 0.2 \text{ cm}^{-3}$<br>$e = 500 \pm 15 \text{ \AA}$<br>$X_{\text{AlAs}} = 0.21 \pm 0.02$ |

| AlGaAs             | $e = 22.6 \pm 5.65 \text{ \AA}$<br>$X_{\text{AlAs}} = 0.21 \pm 0.02$                                   |

| C GaAs             | $e = 300 \pm 30 \text{ \AA}$                                                                           |

| B(Ga/AlGa)As       | $e = 10 \times (20+80) \text{ \AA}$<br>$X_{\text{AlAs}} = 0.21 \pm 0.02$                               |

| B GaAs             | $e = 5000 \pm 150 \text{ \AA}$                                                                         |

| Substrat GaAs S.I. |                                                                                                        |

Fig 5 : HEMT epitaxial growth structure

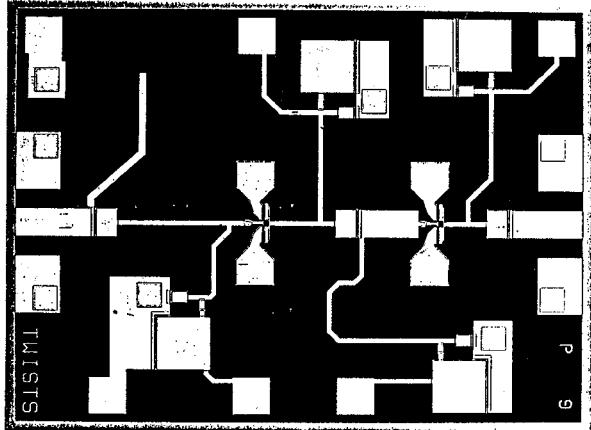

Figure 6 shows a photograph of the 35 GHz circuit. The chip size of Q and V band circuits including bias circuitry and DC block capacitances is 1 mm x 1.5mm.

Fig 6 : Photograph of the 35 GHz amplifier

#### EXPERIMENTAL RESULTS

The amplifiers were first measured on-wafer up to 60 GHz. The on-wafer S parameter measurements consists of a Wiltron 360 vector network analyser, and 65 GHz Cascade Microtech probes mounted on an automatic probing System Electroglass 1034. Accurate calibration is achieved in the full band 1-60 GHz using either the TRL and the LRM techniques.

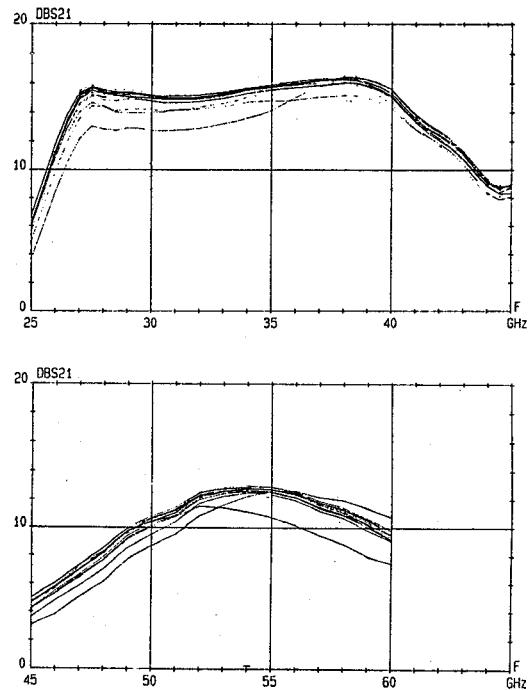

Figures 7 and 8 show the results of the measurements and demonstrate the high yield. The gain is 15.5 dB over 40% frequency range for the 35 GHz amplifier. The 60 GHz amplifier exhibits 12 dB  $\pm$  1 dB gain over 10% frequency range. More over, the amplifiers are well stabilized on low frequencies.

Fig 7, 8 : On-wafer measurements of the Q and V band amplifiers

The circuits were also measured in test fixtures, using Wiltron K connectors for 35 GHz amplifiers, and V connectors for the 60 GHz version. The set up consists essentially of a HP 8970 B noise figure meter and a Hughes noise source.

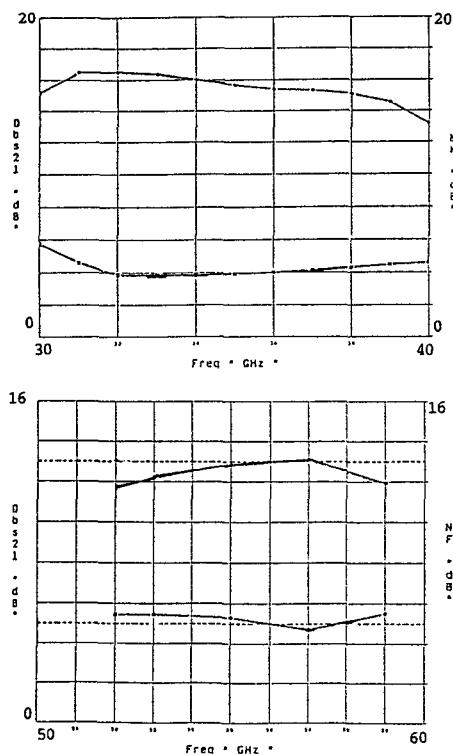

Figure 9 and 10 show the noise performances of both amplifiers. Between 32 GHz and 38 GHz, the gain including test fixture losses is more than 15 dB with less than 4.5 dB noise. Between 53 and 60 GHz, the amplifier has 12.5 dB  $\pm$  0.5 dB gain with 4.5 to 5.5 dB noise figure and 75 mW maximum dissipated DC power.

Fig 9, 10 : Noise Figure and Associated Gain Measurements of the 35 GHz and the 60 GHz Amplifiers

A frequency shift of about 4 GHz can be observed between the on-wafer measurements and those mounted in jigs, for 60 GHz amplifier. This shift was clearly detected during the design. It is simply due to the parasitic elements of the connecting wires.

### CONCLUSION

The experimental results show high performance, high yield ( $\approx 80\%$ ) (no critical elements) and are very suitable for civil low cost applications. During the design, a special effort was made to improve the stabilisation of low noise amplifiers at low frequencies, by damping with the RC circuits and the associated bonding wire. This is essential for its integration in a whole module.

### REFERENCES

- [1] J. YONAK I, M. AUST, K. NAKANO, G, DOW, L.C.T., LIV, E. HSIEH, R. DIA and H.C. YEN

A Q-Band Monolithic three-stage amplifier

1988, IEEE MMWMCS pp91-94

- [2] M. AUST, J. YONAKI, K. NAKANO, J. BERENZ, G.S. DOW, L.C.T. LIV

A family of InGaAs/AlGaAs V. Band Monolithic HEMT LNA's. 1989 GaAs I C Symposium pp95-98

- [3] K.C. GUPTA - R. GARG - R. SHADHA

Computer aided design of microwave circuits - Artech.

### ACKNOWLEDGEMENTS

The authors would like to acknowledge D. DELAGEBEAUDEUF AND C. VERSNAEYEN for their technical support, E. AUBAME for processing, MT. CREISMEAS and M. DOIN for assembly, and E. PARIS and E. ARGINTARU for measurements.

This work was supported by DRET administration.